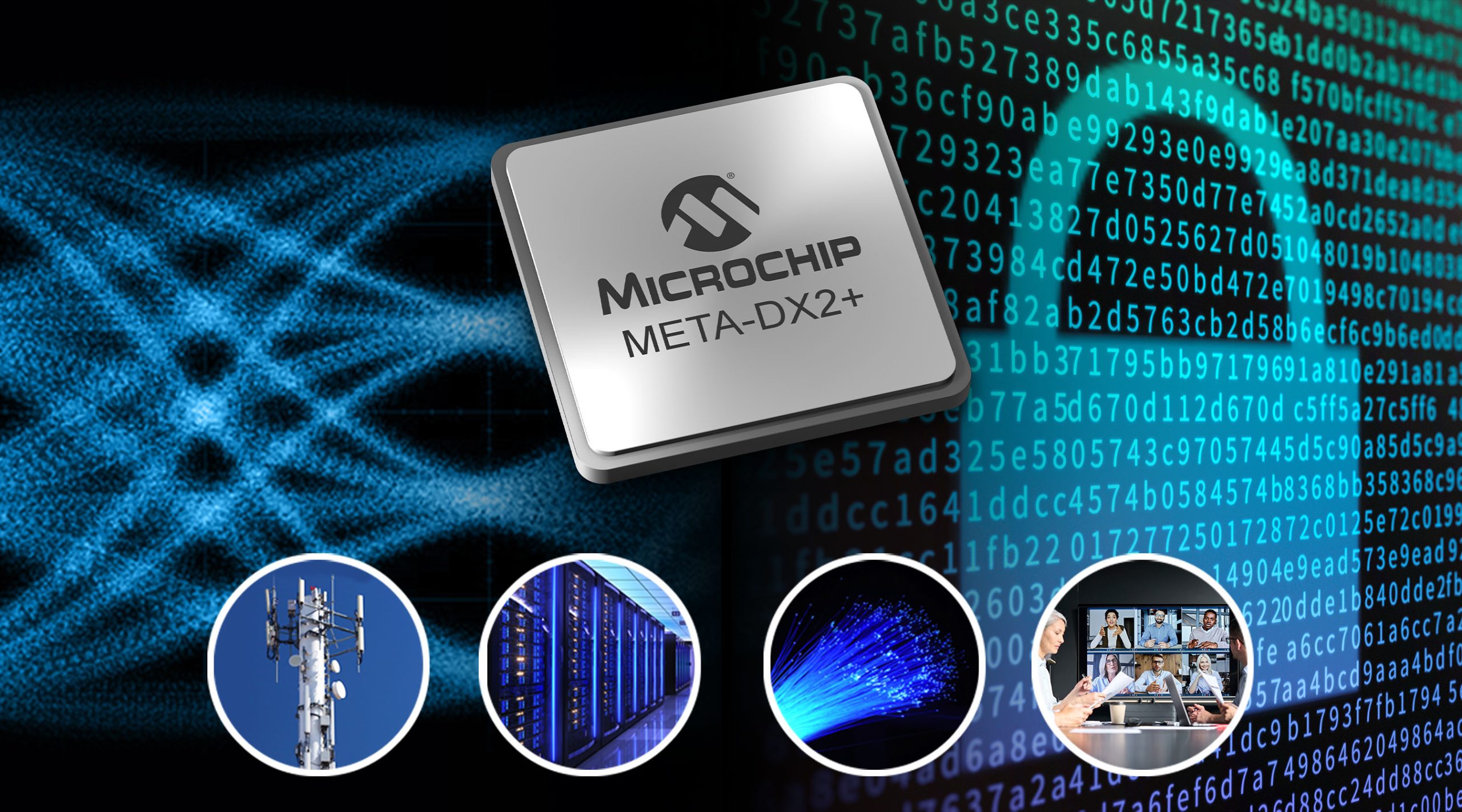

La demanda de mayor ancho de banda y seguridad en la infraestructura de red impulsada por el crecimiento del trabajo híbrido y la distribución geográfica de las redes está redefiniendo las redes sin fronteras. Liderado por aplicaciones AI/ML, se prevé que el ancho de banda total del puerto para 400G (gigabits por segundo) y 800G crezca a una tasa anual de más del 50 %, según 650 Group. Este espectacular crecimiento está ampliando la transición a la conectividad 112G PAM4 más allá de los conmutadores y enrutadores de centros de datos en la nube y proveedores de servicios de telecomunicaciones a plataformas de conmutación Ethernet empresarial. Microchip Technology Inc. (NASDAQ: MCHP) está respondiendo a esta inflexión del mercado con la cartera META-DX2 Ethernet PHY (capa física) al presentar una nueva familia de META-DX2+ PHY.

Estas son las primeras soluciones de la industria configuradas para integrar 1,6 T (terabits por segundo) de cifrado de extremo a extremo de velocidad de línea y agregación de puertos para mantener el espacio más compacto en la transición a la conectividad 112G PAM4 para conmutadores Ethernet empresariales, dispositivos de seguridad, enrutadores de interconexión en la nube y sistemas de transporte óptico. “La introducción de cuatro nuevos META-DX2+ Ethernet PHY demuestra nuestro compromiso de respaldar la transición de la industria a la conectividad 112G PAM4 impulsada por nuestro retemporizador META-DX y cartera PHY. Junto con nuestro retemporizador META-DX2L, ahora ofrecemos un chipset completo para todas las necesidades de conectividad, desde retemporización, caja de cambios hasta funcionalidad PHY avanzada”, dijo Babak Samimi, vicepresidente corporativo de la unidad comercial de comunicaciones de Microchip. “Al ofrecer compatibilidad de huella tanto de hardware como de software, nuestros clientes pueden aprovechar los diseños arquitectónicos en sus sistemas de conmutación y enrutamiento de empresa, centro de datos y proveedor de servicios que pueden ofrecer la habilitación de funciones avanzadas de pago según las necesidades, que incluyen seguridad, agregación de puertos de múltiples tasas y sellado de tiempo de precisión a través de un modelo de suscripción de software”. La arquitectura de ruta de datos 1.6T configurable de META-DX2+ supera a los siguientes competidores cercanos por 2 veces en la capacidad total de la caja de cambios y los modos mux de interruptor de protección 2:1 sin golpes habilitados por su capacidad única ShiftIO.

Las capacidades flexibles de agregación de puertos XpandIO optimizan la utilización del puerto del enrutador/conmutador cuando se admite tráfico de baja velocidad. Además, los dispositivos incluyen compatibilidad con el Protocolo de tiempo de precisión (PTP) IEEE® 1588 Clase C/D para el sellado de tiempo preciso en nanosegundos requerido para 5G y servicios empresariales críticos. Al ofrecer una cartera de retemporizadores compatibles con la huella y PHY avanzados con opciones de cifrado, Microchip permite a los desarrolladores ampliar sus diseños para agregar MACsec e IPsec basados en un diseño de placa común y un kit de desarrollo de software (SDK). Las capacidades diferenciadas de META-DX2+ incluyen: Doble 800 GbE, cuádruple 400 GbE y 16x 100/50/25/10/1 GbE MAC/PHY Motores MACsec/IPsec de 1,6 T integrados que descargan el cifrado de los procesadores de paquetes para que los sistemas puedan escalar más fácilmente a anchos de banda más altos con seguridad de extremo a extremo

Más del 20 % de ahorro en la placa en comparación con las soluciones de la competencia que requieren dos dispositivos para ofrecer la misma caja de cambios de 1,6 T y modos mux 2:1 sin hits XpandIO permite la agregación de puertos de clientes Ethernet de baja velocidad a través de interfaces Ethernet de mayor velocidad, optimizadas para plataformas empresariales.

La función ShiftIO combinada con un punto de cruce integrado altamente configurable permite una conectividad flexible entre interruptores, procesadores y ópticas externos Variantes de dispositivos con 48 o 32 Long Reach (LR) con capacidad 112G PAM4 SerDes que incluyen capacidad de programación para optimizar la potencia frente al rendimiento Compatibilidad con Ethernet, OTN, Fibre Channel y velocidades de datos patentadas para aplicaciones AI/ML “A medida que la industria hace la transición a un ecosistema serial 112G PAM4 para enrutadores y conmutadores de alta densidad, el cifrado de velocidad de línea y el uso eficiente de la capacidad del puerto se vuelven cada vez más importantes”, dijo Alan Weckel, fundador y analista de tecnología de 650 Group, LLC. “La familia META-DX2+ de Microchip desempeñará un papel importante al habilitar el cifrado MACsec e IPsec, optimizar la capacidad del puerto con la agregación de puertos y conectar de manera flexible el silicio de enrutamiento/conmutación a ópticas de 400G y 800G de velocidad múltiple”. Al igual que el retemporizador META-DX2L, la nueva serie de META-DX2+ PHY se puede usar con los FPGA PolarFire® de Microchip, el PLL de alto rendimiento ZL30632, osciladores, reguladores de voltaje y otros componentes que han sido previamente validados como un sistema para ayudar acelerar los diseños en producción.

Herramientas de desarrollo

El SDK Ethernet PHY de segunda generación de Microchip para la familia META-DX2 reduce los costos de desarrollo con bibliotecas API y firmware probados en campo. El SDK es compatible con todos los dispositivos META-DX2L y META-DX2+ PHY dentro de la familia de productos. Se incluye compatibilidad con las extensiones PHY de la interfaz de abstracción de conmutación (SAI) de Open Compute Project (OCP) para habilitar la compatibilidad agnóstica de META-DX2 PHY dentro de una amplia gama de sistemas operativos de red (NOS) compatibles con SAI.

Más información:

https://www.microchip.com/en-us/products/high-speed-networking-and-video/ethernet/ethernet-phys/meta-dx-family?utm_medium=CTA&utm_campaign=METADXFamily